近日,德国波鸿鲁尔大学和Max Planck网络安全与隐私研究所的研究人员合作在安全顶会usenix security 2020上发表了一篇名为The Unpatchable Silicon: A Full Break of the Bitstream Encryption of Xilinx 7-Series FPGAs的论文。在论文中,研究人员称在赛灵思(Xilinx)可编程逻辑产品中发现了一个不可修复的硬件漏洞,攻击者利用该漏洞可以破坏比特流加密、克隆知识产权、修改功能、甚至注入硬件木马。

研究人员称,利用该设计漏洞可以泄露解密的比特流。在攻击中,FPGA用作解密Oracle,只需要访问配置接口就可以了。攻击并不需要复杂的工具,根据目标系统的不同,攻击者甚至可以远程发起攻击。攻击的复杂性与DPA攻击类似。

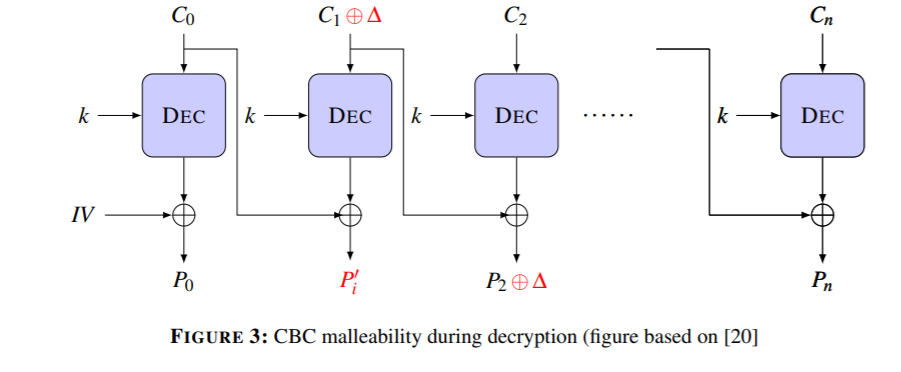

利用CBC模式来加密和解密任意区块

FPGA是一种可编程的集成电路,用户可以根据不同的配置模式,采用不同的编程方式。因此,FPGA的使用非常灵活,也被广泛应用于5G网络、消费电子产品、数据中心、航空、自动驾驶技术等的开发中。FPGA市场基本上被赛灵思和Intel(Altera)两家巨头平分了,其中赛灵思的市场份额接近50%。FPGA设计编码在不同流中,因此硬件漏洞会带来非常严重的后果。

与其他针对赛灵思和Intel(Altera) FPGA的侧信道和探测攻击相比,研究人员的漏洞攻击是非常低成本的,可以利用SelectMAP、JTAG这样的配置接口来从FPGA设备中恢复和修改比特流。

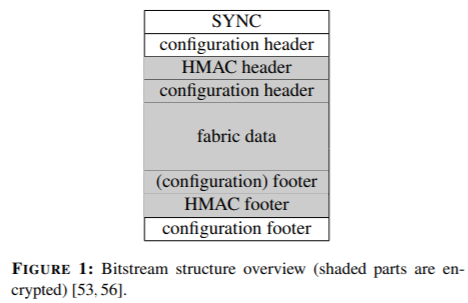

比特流结构

"readback"(回读)是一种可以帮助验证设计是否正确下载到设备中的特征。为了保护设计,比特流是用AES-256用CBC模式加密的,可以预防来自外部接口的回读。研究人员通过设计的攻击可以操作加密的比特流来重定向解密的配置数据到MultiBoot的开始地址寄存器,允许在远程更新on the fly镜像之间切换,价值回读比特流和设计好的设计到FPGA设备中。

但是由于使用flash内存来保存这些组件,reset(复位)并不会清空寄存器中的内容。最终导致比特流的机密性被破坏:

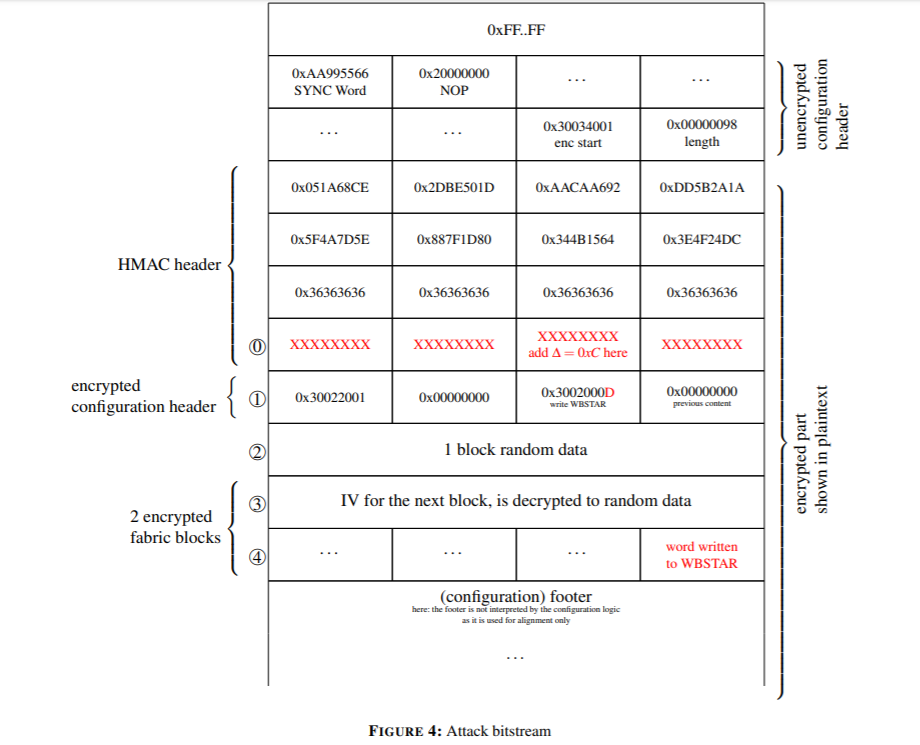

1、创建恶意比特流和回读比特流。恶意比特流利用CBC模式的扩展性来改变比特流中的命令,来将数据写入WBSTAR配置寄存器中。

2、加载恶意比特流到FPGA设备中。

3、由于第1步中的比特流的变化会导致FPGA自动复位,但是不会复制WBSTAR的内容。

4、使用回读比特流回读WBSTRA寄存器中的内容。

5、手动复位FPGA设备来重复以上步骤,恢复完整的加密比特流——32位的字。

总的来说,如果用加密key加载,FPGA就会解密加密的比特流,并将其写入可读的配置寄存器中。因此,FPGA是用作解密Oracle。由于每个循环中只能恢复32位的字,这决定了解密整个比特流所需的时间:研究人员在实验中发现可以在3小时42分钟恢复完成的Kintex-7 XC7K160T 比特流。

在破坏真实性的攻击中, FGPA可以用来加密任意的比特流和创建有效的消息认证码(HMAC),以打破比特流的真实性。

研究人员称,这些攻击其实来源于一个陷阱,即加密的比特流header的数据会在被验证之前进行解释,从而允许恶意比特流在FPGA的逻辑结构上运行。

漏洞无法修复

由于这些攻击是基于协议中的漏洞,研究人员称在不对FPGA硬件重新设计的情况下对安全协议的任何修改都是不可能的。由于无法对加密协议的底层芯片进行修复,因为研究人员认为该攻击非常严重。而且7系芯片在FPGA市场占有很大的份额,因此几乎不可能替换这些设备。

研究人员已于9月24日将相关漏洞报告给了赛灵思,赛灵思也认可了该漏洞,并发表了致谢。

完整论文参见:https://www.usenix.org/system/files/sec20fall_ender_prepub.pdf

本文翻译自:https://thehackernews.com/2020/04/fpga-chip-vulnerability.html如若转载,请注明原文地址

如有侵权请联系:admin#unsafe.sh